#### **Eindhoven University of Technology**

| ٨ | Л | ٨ | G. | т | D |

|---|---|---|----|---|---|

| n | Л | А |    |   | ĸ |

Professionalizing hardware-based memory acquisition for incident response scenarios cold boot using Coreboot and the Intel memory scrambler

van Heijningen, N.

Award date: 2017

#### Disclaimer

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

#### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 23. Nov. 2017

### PROFESSIONALIZING HARDWARE-BASED MEMORY ACQUISITION FOR INCIDENT RESPONSE SCENARIOS

#### COLD BOOT USING COREBOOT AND THE INTEL MEMORY SCRAMBLER

#### Master's Thesis

Author:

Nico van Heijningen

0893377

Supervisors: Lejla Batina Boris Škorić Ruud Schramp

Volatile memory may contain many traces important in a forensic investigation. When the odds are stacked against a forensic investigator he may have to resort to innovative memory acquisition methods. In this work we present an evaluation of the forensic soundness of different memory acquisition methods based on their applicability in a near worst-case scenario. Furthermore, we discuss the details of an acquisition method we developed based on Coreboot and the cold boot attack. It is shown that the method developed is correct to a far higher degree than related methods, and that the method's integrity is directly related to the susceptibility of specific memory modules to the remanence effect. The observation that the cold boot attack is not as consistent as anticipated has been an unexpected result. Finally, research into the Intel memory scrambler of the Ivy Bridge microarchitecture is put forth. We show that it is feasible to reproduce the working of the memory scrambler based on only 1026 bits of data and provide a detailed analysis of its working.

#### CONTENTS

| 1  | INTR     | CODUCTION 1                                      |

|----|----------|--------------------------------------------------|

|    | 1.1      | Problem description 1                            |

|    | 1.2      | Scope 1                                          |

|    | 1.3      | Scientific question 2                            |

|    | 1.4      | Contribution 2                                   |

| Ι  | LITE     | ERATURE STUDY 3                                  |

| 2  | BACE     | KGROUND 5                                        |

|    | 2.1      | Computer architecture 5                          |

|    |          | 2.1.1 Boot sequence 7                            |

|    | 2.2      | Memory addressing 7                              |

|    |          | 2.2.1 Memory address routing 8                   |

|    |          | 2.2.2 Memory address translation 9               |

|    |          | 2.2.3 The overloading of address terminology 9   |

|    | 2.3      | SDRAM and DDR3 11                                |

| 3  | _        | ATED WORK 15                                     |

| 9  | 3.1      | Methodology for evaluating forensic soundness 15 |

|    | 3.2      | Software 16                                      |

|    | _        | Direct Memory Access (DMA) 16                    |

|    |          | System Management Mode (SMM) 17                  |

|    |          | BIOS modification 17                             |

|    |          | Cold boot 19                                     |

|    | _        | Legal requirements 20                            |

|    | 3.8      | Conclusion 22                                    |

| II | ENG      | INEERING 23                                      |

| 4  | CON      | CEPT AND DESIGN 25                               |

| •  | 4.1      | Concept 25                                       |

|    | •        | Design 26                                        |

| 5  | -        | EBOOT 27                                         |

| ,  |          | Binary situation 27                              |

|    | 5.2      | Memory initialization 27                         |

|    | 5.3      | Cache-as-RAM (CAR) 28                            |

| 6  | IMPI     | LEMENTATION DETAILS 29                           |

|    | 6.1      | Exfiltration routes 29                           |

|    | 6.2      | Accessing all memory 30                          |

|    |          | Memory integrity concerns 31                     |

|    | 6.4      | Reproducibility 32                               |

| 7  | •        | DATION 33                                        |

| •  | 7.1      | Experiment methodology 33                        |

|    | ,<br>7.2 | Cooling techniques 33                            |

|    | 7.3      | Discussion of empirical results 34               |

```

Correctness

7.4

35

Integrity

7.5

35

7.6

Conclusion

36

III RESEARCH

37

BACKGROUND & GOALS

Background

8.1

8.2

Goals

PRIOR & RELATED WORK

43

9.1

Prior work

43

Related work

9.2

43

10 REVERSE ENGINEERING

10.1 PRBS acquisition methods

10.1.1 Differential PRBS acquisition

47

10.1.2 Plain PRBS acquisition

10.1.3 Differential PRBS vs. plain PRBS

48

10.2 PRBS internal structure definitions

10.3 SCRMLO and SCRMHI

51

10.4 Reproducing the PRBS

51

10.4.1 Address based scrambling

10.4.2 SCRMSEED based scrambling

53

10.4.3 PRBS LFSR stretches

56

11 REMAINING PROBLEMS AND CONCLUSION

61

FUTURE WORK & CONCLUSION

63

12 FUTURE WORK

65

13 CONCLUSION

67

V

APPENDICES

69

EXPERIMENTAL SETUP

Α

71

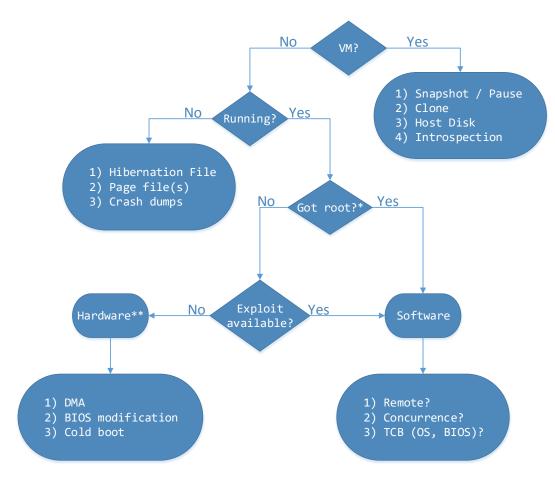

FLOWCHART - MEMORY ACQUISITION OPTIONS

В

C

HANDBOOK FOR THE FORENSIC INVESTIGATOR: APPLI-

CATION OF THE COLD BOOT USING COREBOOT METHOD

77

INTEL ME

79

D

81

\mathbf{E}

NULL PRBS

REPRESENTATION OF SCRMLO & SCRMHI IN MEMORY

85

F

OVERLAPPING STREAMS

87

BIBLIOGRAPHY

93

```

#### LIST OF FIGURES

CPU

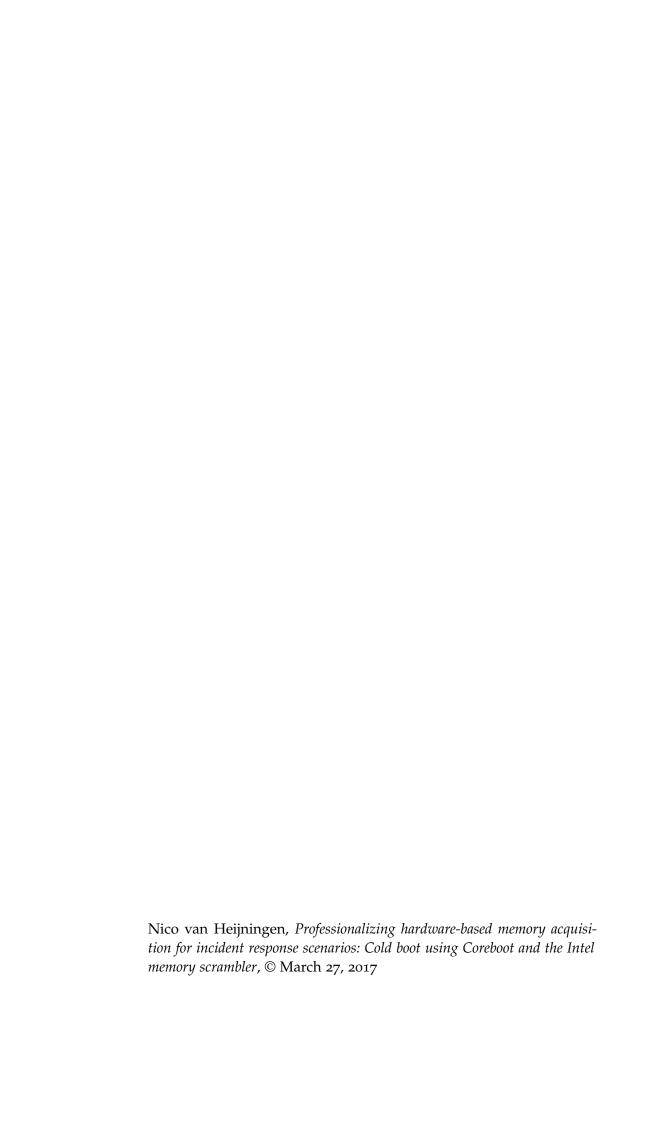

| Figure 1  | Motherboard architecture 6                            |

|-----------|-------------------------------------------------------|

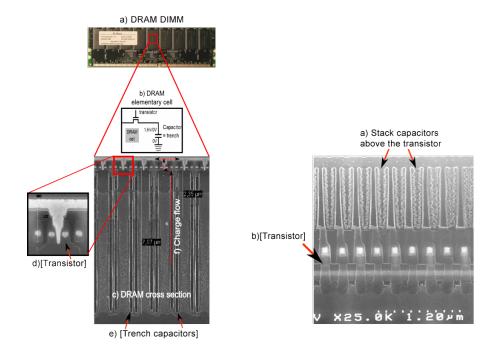

| Figure 2  | Layout of memory 10                                   |

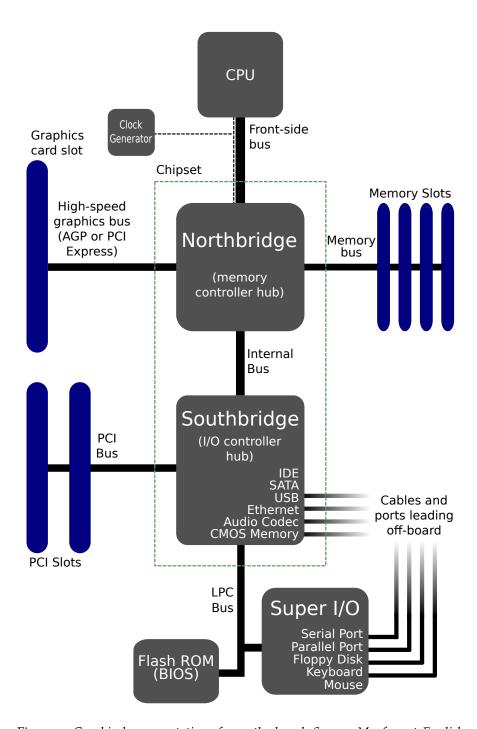

| Figure 3  | Capacitors 12                                         |

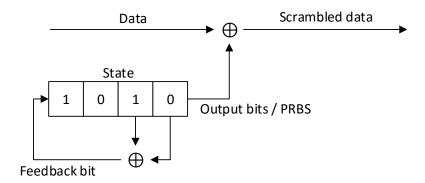

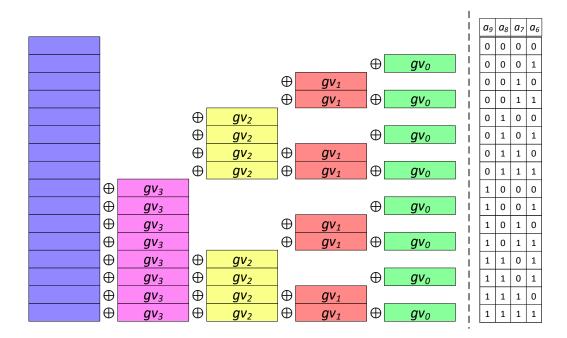

| Figure 4  | Typical scrambler 40                                  |

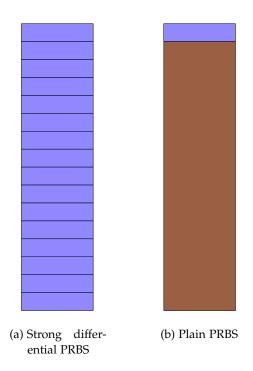

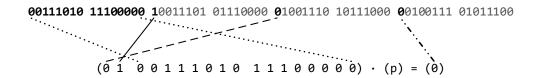

| Figure 5  | Differential vs. plain PRBS acquisition 48            |

| Figure 6  | Strong differential PRBS vs. plain PRBS 50            |

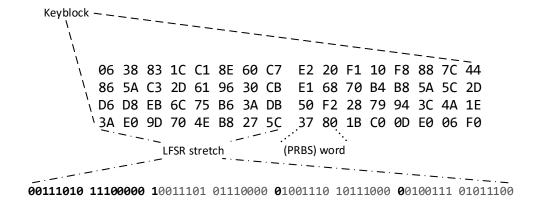

| Figure 7  | Keyblock internals 51                                 |

| Figure 8  | Plain PRBS 54                                         |

| Figure 9  | Obtaining 18-bit LFSR state 59                        |

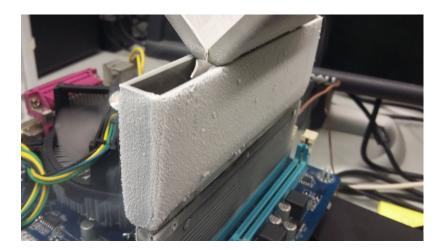

| Figure 10 | Setup 72                                              |

| Figure 11 | Frost 72                                              |

| LIST OF T | ABLES                                                 |

|           |                                                       |

| Table 1   | List of DIMMs 73                                      |

| LIST OF L | ISTINGS                                               |

| Listing 1 | Definition of scrambling seeds in Coreboot 44         |

| ACRONY    | MS                                                    |

| ASCII     | American Standard Code for Information<br>Interchange |

| BAR       | Base Address Register                                 |

| BIOS      | Basic I/O System                                      |

| BIST      | Built-In Self Test                                    |

| BM        | Berlekamp-Massey                                      |

| CAR       | Cache-as-RAM                                          |

| CDMA      | Code Division Multiple Access                         |

Central Processing Unit

**DDR** Double Data Rate

**DIMM** Dual In-line Memory Module

**DMA** Direct Memory Access

**ECC** Error-Correcting Code

**FPGA** Field-Programmable Gate Array

GCC GNU Compiler Collection

**GPT** GUID Partition Table

GUID Globally Unique Identifier

I/O Input/Output

ME Management Engine

IOMMU I/O Memory Management Unit

JEDEC Joint Electron Device Engineering Council

LFSR Linear-Feedback Shift Register

MBR Master Boot Record

MCH Memory Controller Hub

MMIO Memory Mapped I/O

MMU Memory Management Unit

MTRR Memory Type Range Register

NDA Non-Disclosure Agreement

**NFI** Netherlands Forensic Institute

**OS** Operating System

PAE Physical Address Extension

PCB Printed Circuit Board

PCIe Peripheral Component Interconnect express

PCI Peripheral Component Interconnect

**PCMCIA** Personal Computer Memory Card International

Association

PIO Programmed I/O

**POST** Power-On Self-Test

**PRBS** Pseudo-Random Binary Sequence

RAM Random-Access Memory

SATA Serial Advanced Technology Attachment

SDRAM Synchronous Dynamic Random-Access Memory

SMM System Management Mode

**SODIMM** Small Outline DIMM

**SPD** Serial Presence Detect

SSD Solid-State Drive

TCB Trusted Computing Base

TLB Translation Lookaside Buffer

**TOLUD** Top of Low Usable DRAM

**UEFI** Unified Extensible Firmware Interface

**USB** Universal Serial Bus

VGA Video Graphics Array

INTRODUCTION

Computers use memory to save their state. Different types of memory are used to save different states. Depending on the speed of state transitions, the data is either saved in the processor caches, Random-Access Memory (RAM), or on the hard drive. The ability to inspect the state of a computer is of great importance in the field of computer forensics. This state may prove to be meaningful evidence in a subsequent investigation. A complicating matter is that not all memory retains its state when power is removed, it is then said to be volatile. Contemporary RAM being the main example, it returns to a predefined ground state after power is lost. In general, the manner in which to acquire a computer's memory becomes increasingly more difficult as its physical size decreases and volatility increases. This work therefore, focuses on extraction of data from RAM while a computer is (still) switched on.

#### 1.1 PROBLEM DESCRIPTION

How to acquire all memory of a locked, yet powered on computer from a uncooperative user? That is, a (near worst-case) incident response scenario where: no privileges are available (locked computer); the machine is fully patched (no exploits available); the risk that antiforensic measures may be in place (full-disk encryption); and a Basic I/O System (BIOS) that clears the memory on reset. Furthermore, we assume that, physical access to the device is possible (no need for remote acquisition), yet no previous interaction has been possible (no opportunity for pre-installation).

#### 1.2 SCOPE

To scope the project into a manageable size for the time frame set, it was chosen to focus on obtaining a flat linear copy of the physical DDR3 memory of a predefined desktop system (see Appendix A). As a consequence, this work focusses solely on Intel hardware. Furthermore, as the analysis of an obtained physical memory image allows for a whole study on itself, no other requirements on post-processing or carving logical data structures out of the obtained physical data have been defined.

#### SCIENTIFIC QUESTION

Taking into account the problem description, four scientific questions have been defined.

- What memory acquisition methods are available and applicable in this scenario?

- How can the most suitable method be professionalized for use in a forensics lab?

- How forensically sound is the method of choice?

- What is the effect of the memory scrambling mechanism as implemented by Intel?

#### CONTRIBUTION

The contribution of this thesis is threefold:

- I. A review of the acquisition methods available in a near worstcase incident response scenario is presented in Part I.

- II. The implementation of a novel memory acquisition method is discussed in Part II.

- III. An analysis of the Intel memory scrambler is provided in Part III.

## Part I LITERATURE STUDY

2

In order to aid in the understanding of this thesis, a discussion on the underlying concepts is presented in this chapter. It should be understood that some generalization is in order, to allow for a concise, yet self-contained section. A more detailed discussion of recent Intel computer architectures may, for example, be found in [11].

#### 2.1 COMPUTER ARCHITECTURE

In general, personal computers are built from different components, all of which need to function in harmony. A main Printed Circuit Board (PCB), named the motherboard, houses all the parts (see Figure 1). The components communicate through hardware buses, which consist of a certain number of parallel wires called traces on the PCB. On top of the buses run different signalling protocols. The main components are the: Central Processing Unit (CPU), RAM, and different Input/Output (I/O) peripherals. The latter of which are made available through a multitude of different ports. For example, Universal Serial Bus (USB) to connect general peripherals, Video Graphics Array (VGA) to connect monitors, Serial Advanced Technology Attachment (SATA) to connect hard disks, and Ethernet for networking.

The manner in which components are connected and communicate differs between hardware generations and models. In general there are two main components responsible, the northbridge and the southbridge, which together can be identified as the chipset. The northbridge or Memory Controller Hub (MCH), is connected with a fast bus to the processor, it determines where memory addresses are routed, and is responsible for fast communication between the: processor, memory and expansion buses such as Peripheral Component Interconnect express (PCIe). The southbridge is responsible for the communication between peripherals and the northbridge. Whereas older hardware used to have components physically placed centimeters apart due to their size and heat restrictions, recent developments focus on placing more components on a single chip. For example, in most modern CPUs, the communication with the main memory is now handled by logic placed on the same silicon die as the CPU cores. So the clear boundaries between the: CPU, northbridge, and southbridge have faded.

A general x86 instruction set compatible CPU consists of registers, caches, and (multiple) processing cores. The registers save the state of the processor, the caches buffer (recently requested) data from main-

Figure 1: Graphical representation of a motherboard. Source: Moxfyre at English Wikipedia

memory, and the cores perform operations on the data. There may be different levels of cache with different purposes e.g. an instruction cache and a data cache. For more details on the x86 architecture we kindly refer to [31].

Contemporary main-memory or RAM is generally packaged in the form of Dual In-line Memory Modules (DIMMs), of the Synchronous Dynamic Random-Access Memory (SDRAM) type and based on one of the four Double Data Rate (DDR) standards (DDR1 through DDR4 [34, 35, 37, 38]) defined by the Joint Electron Device Engineering Council (JEDEC). DDR3, on which we focus, is discussed in more detail in Section 2.3.

#### 2.1.1 Boot sequence

When a computer is started, it goes through a boot sequence, initializing all connected hardware to a working state such that an Operating System (OS) can be started. The first code a computer executes is located at the reset vector. This is a memory address which is generally routed to a non-volatile memory chip where firmware and BIOS code is saved. After executing the firmware and BIOS or Unified Extensible Firmware Interface (UEFI) code, the Master Boot Record (MBR) or GUID Partition Table (GPT) is loaded, which is usually located on a hard disk. This invokes the bootloader which loads the kernel. As soon as the kernel and other OS specific components have finished loading, user applications may be started.

#### 2.2 MEMORY ADDRESSING

The location of data in RAM is defined by its address. Each memory address points to a single byte of data and the address bus is the physical representation of a memory address. The width of the address bus determines the length of the memory addresses and therefore the maximum number of possible addresses<sup>1</sup>. In turn limiting the amount of memory that can be used by a system. For example, addresses of 32 bits allows for four gigabytes of data to be located<sup>2</sup>. When more than four gigabytes of memory is to be used, a 32 bit wide address bus by itself is insufficient.

Over the course of time, the desire for speed and backwards compatibility has led to the introduction of different processor execution modes. Each of those modes allows a processor to address more memory. Mainly due to legacy reasons, older modes are still supported by newer CPUs. *Real mode* is the 16 bit legacy mode all x86 processors start in. Only a single megabyte of memory is addressable in this

<sup>1</sup> Multiplexing reserved.

$<sup>^{2}</sup>$   $^{232}$  addresses can point to 4294967296 bytes / 1024 (KiB) / 1024 (MiB) / 1024 (GiB) = 4 GiB

mode. *Protected mode* is the native operation mode of the 32 bit x86 instruction set. *Long mode* is the native operation mode of the 64 bit x86 instruction set, and allows more than four gigabyte of memory to be addressed.

Next to these legacy modes, *System Management Mode (SMM)* was introduced. SMM transparently suspends normal execution to allow for an isolated execution environment, mainly used for power management and system security by the system's firmware. Again we refer to [31, Chapter 3 - Basic execution environment] for a more detailed discussion.

As memory acquisition requires reading all of the memory physically present on the DIMMs, there are two artifacts of these (legacy) modes that have to be taken into account: memory address routing and translation.

#### 2.2.1 Memory address routing

Not all memory addresses may point to data in the physical DIMMs: ranges of memory can be routed to other components. Examples of mechanisms that cause memory addresses to be routed to different components are: Memory Mapped I/O (MMIO), Memory Type Range Register (MTRR), and static routing. MMIO maps the memory of peripherals (I/O devices) into the computer's address space. The use of MMIO allows the memory of e.g. a network card to be accessed through regular memory operations. To enable MMIO the BIOS configures the processor's Top of Low Usable DRAM (TOLUD) register with a memory address above which all memory accesses (up to the 4 GiB limit) are reserved for MMIO. The Base Address Registers (BARs) of e.g. PCI peripherals can be programmed such that those devices may respond to reads and writes to data in the MMIO range. The MMIO area is thus not backed by actual RAM. MTRRs control how ranges of memory addresses are cached. For example, they determine when an update of the cache is written back to RAM. MTRRs are used to enable Cache-as-RAM (CAR) (discussed in Section 5.3) and are discussed in more detail in [11]. MTRRs may hence cause certain reads from memory to be read from the cache only, instead of the actual RAM. Finally, the memory addresses near the reset vector may be statically routed to the BIOS chip, as in that point of the boot sequence, other hardware has yet to be initialized.

Furthermore, sequential memory accesses may be distributed over different components through the routing mechanism. For example, CPUs may include options to interleave memory accesses on the granularity most suitable for performance increase [56] and [28, 2.1.3.2.1 Dual-Channel Symmetric Mode]. By routing, for example, sequential memory addresses to different DIMMs these accesses can be pipelined and thus retrieved concurrently. Figure 2 shows an exam-

ple of the routing behavior of a computer with two DIMMs installed. It highlights the difference in the resulting linear copy of memory, between the case when no interleaving is applied and when the memory addresses are distributed in an interleaving fashion across the two DIMMs (on a RAM chip granularity). The address at which a specific region of memory starts can be altered by setting registers in the MCH. Many different regions of memory have been ascribed a specific purpose. For example, the legacy region of Figure 2 includes many smaller regions with each a different purpose. To prevent a lengthy discussion of the historical reason of existence of every single memory region, we kindly refer to the datasheets of the hardware ([28] in our case).

One important aspect of different memory regions in the context of memory acquisition are the so-called 'stolen' memory regions. These regions of memory are used by components to save their state. Examples of components using stolen regions are: the integrated graphics device, SMM, and the Intel Management Engine (ME) (for details on the latter we refer to Appendix D). Instead of using their own internal memory, the RAM is used for this. However, the regions are allocated, to the components, very early in the boot sequence, and may be routed to allow the components exclusive access. This might be the cause of serious concerns when acquiring memory; a point which we will return to in Section 6.3.

#### 2.2.2 Memory address translation

A memory address may, over the course of time, translate to different locations in physical RAM. The main mechanism that introduces such translation is called paging. Next to providing isolation between code and data, paging can also be used to provide virtual memory. Virtual memory allows a computer to use more memory than actually exists, by saving lesser used parts of memory to slower memory (e.g. the hard disk). Paging introduces the distinction between logical and physical addresses. Logical (virtual) addresses are used by the code whereas the physical addresses are the locations the data is actually stored. When a logical address is accessed that does not actually reside in RAM, the OS first puts the address's data in memory before continuing execution of the program. Because the logical address space is far larger than the physical address space, over time the same logical address may point to different physical addresses.

#### 2.2.3 The overloading of address terminology

The consequence of the above sections memory address routing and translation is that some literature attributes different meanings to the term 'physical memory address'. Overloading the term by using it

Figure 2: Memory layout of a typical computer with two DIMMs installed. Memory routing is applied irrespective of interleaving being applied. Due to reasons of visibility, not all regions use the same scale.

both in the context within the host and in the context of communication over the memory bus (between the host and the DIMM).

On the host side, the logical addresses are used to address virtual memory, and are translated by the Memory Management Unit (MMU) –using the paging mechanism– to physical host addresses. The Translation Lookaside Buffer (TLB) is used to cache a number of these translations to increase the mechanism's speed. The physical host addresses are next converted by the MCH to physical DIMM addresses, for example, DDR3 commands and send over the physical memory bus. When not obvious from the context we will prepend the term 'physical address' with either host or DIMM to remove ambiguity.

#### 2.3 SDRAM AND DDR3

There are many different types and generations of volatile memory. This work focusses solely on DDR3 Synchronous Dynamic Random-Access Memory (SDRAM). The 'synchronous' in SDRAM means that all memory works based on a single clock, whereas 'dynamic' stands for the fact that the memory needs to be refreshed (the cause for its volatile property). SDRAM needs to be refreshed, as each memory cell consists of a capacitor and transistor. The transistor controls whether power can flow to/from the capacitor and the capacitor holds the memory cell's state. The cell's state is determined by the difference between a threshold value and the charge saved in the capacitor. Even when the transistor prevents charge to flow to/from the capacitor, the charge still gradually leaks to/from the capacitor. Details on the underlying physical properties regarding this leakage can, for example, be found in [21]. Once a memory cell's state can no longer be determined it is said to be in it ground state. The cell's ground state may either be a zero or one depending on whether the memory cell's capacitor is wired to power or ground. To prevent this, all capacitors need to be recharged before any of the cells' states can no longer be determined correctly. The leaking of the charge of a capacitor is called decay, and its counterpart is called remanence. The time a cell's state can correctly be determined without a refresh is named its remanence time or period. The remanence period is lower bounded by the DDR3 specification [37], defining that a refresh command is to be sent every 7.8 µs. Depending on the memory's density, typically every capacitor is required to have a minimum remanence period of 64 ms. Figure 3 shows cross sections of two different types of capacitors present inside SDRAM chips. Trench capacitors are an older technology which relatively take up more space on the silicon than stacked capacitors. The chronological development of SDRAM capacitors is discussed in [66] and an analysis of the capacitors used in contemporary SDRAM chips are provided in [40].

Figure 3: Different physical appearances of capacitors. Trench capacitors are shown left (planar view), stacked capacitors are shown right (cross-section). Source: http://www.sdram-technology.info/sdram-cross-section.html

The DDR3 specification [37] supports a plethora of different variants and extensions, providing SDRAM manufactures the room to innovate. Innovations are typically related to advances in integrity, speed, and power consumption. Due to reasons of conciseness and relevance, we refrain from providing a complete overview of all options and their details. However, many of these advances have been standardized by JEDEC and some of the different options that may be encountered are: speed (frequencies, timings); integrity (registered (RDIMM), fully buffered (FBDIMM), load reduced (LRDIMM), Error-Correcting Code (ECC)); power usage (DDR3L (low voltage), DDR3U (ultra low voltage)); and form factor (Dual In-line Memory Module (DIMM), SODIMM (small outline), LPDIMM (low profile), VLPDIMM (very low profile)). Each memory module is labeled, the contents of this label is typically standardized by its manufacturer<sup>3</sup>. Most of the aforementioned options should be recognizable on this label. Furthermore, every module contains a small amount of persistent memory, used to save Serial Presence Detect (SPD) information, again standardized by JEDEC [39]. The SPD data includes information regarding the type of DIMM in an electronic format. SPD is used by a computer's memory controller to enable automatic initialization of different types of DIMMs. Not every memory controller may sup-

<sup>3</sup> See for example [42, 49, 60], a preliminary JEDEC specification has also been released but has, to the best of our knowledge, never been standardized [36].

port all types of memory modules. Typically a memory controller only supports one generation of DDR and only higher-end motherboards support integrity enhancing options. A memory controller initializes and communicates with a DIMM by transitioning through the DIMM's internal state machine as defined in the DDR3 standard [37, 3.1 Simplified State Diagram].

The details of SDRAM discussed above lie at the basis of the different factors that influence the cold boot method; as will be discussed in more detail in Section 3.6 and Section 7.3.

#### RELATED WORK

A body of research has been developed on the topic of memory acquisition. Due to some subtle, yet important differences in scope and scenario, not all work fits that of ours. Therefore, different methods of memory acquisition are reviewed; promising methods are presented in more detail. Furthermore, a justification of each method's suitability in our setting is provided. Every justification is accompanied by an evaluation of the method's forensic soundness, based on the following criteria.

#### 3.1 METHODOLOGY FOR EVALUATING FORENSIC SOUNDNESS

The quality of an acquisition method and the data it produces is of great importance in a forensic context. Vömel and Freiling have distilled this idea of forensic soundness (of acquired volatile memory) into three criteria: correctness, atomicity, and integrity [70, 71]. Vömel and Freiling provide a formal definition of the criteria, together with a justification of their independence and claim that satisfying these three criteria implies a forensically sound copy of memory; here we only provide an intuitive description. The acquired memory is deemed forensically sound if it is:

- an exact copy of the data in memory i.e. no data skipped/missed (*correctness*).

- free of any concurrent system activity i.e. other processes are prevented to write to memory (*atomicity*).

- the memory is not modified after a certain point in time i.e. the start of acquisition (*integrity*).

The criteria have been applied to specific implementations by Vömel and Stüttgen [72] and Gruhn [15, Chapter 4], as a whitebox and black-box methodology respectively. Vömel and Stüttgen restricted themselves to software only acquisition methods, and Gruhn has limited his scope by taking correctness for granted. Their work has shown that most memory acquisition methods are only able to fulfill the three criteria up to a certain degree. We have based our evaluation on their findings, but differ our methodology on two points. First, instead of checking the correctness of a region of memory, we explicitly evaluate a method's correctness based only on the question whether it can acquire all memory available. Second, instead of evaluating specific implementations, we aim to review the general acquisition methods in relation to our scenario as defined in Section 1.1; to be able to do this we introduce the following generalization.

Although not explicitly noted by Vömel and Freiling, we argue that their criteria encompass the concept of anti-forensics. Anti-forensics is defined as: "any measure that prevents a forensic analysis or reduces its quality" [15] and therefore the goal of any such measure is to reduce the degree of correctness, atomicity, and integrity. One may argue that the a-priori chance of the presence of anti-forensic measures may be small, based on a risk assessment on the background of the user. However, such an assessment may prove to be difficult to perform or its result to be biased, due to the possible lack of information on a user. We argue that chance of the success of anti-forensic measures is proportional to the size of the Trusted Computing Base (TCB) of the acquisition method and that therefore a method requiring a small TCB is preferred above a method requiring a large TCB.

#### 3.2 SOFTWARE

A multitude of applications have been developed over the years with the aim to secure volatile memory. For all major recent OSes a program can be installed and run to acquire memory. Due to its ease of use and low impact on the stability of the system, we consider software to be a preferred memory acquisition method.

However, the fact that the software runs on the same machine from which the memory needs to be acquired, has two implications. First, the acquisition software alters the state of the machine, as it loads itself in memory, overwriting the data to be acquired. Second, software has the largest TCB possible. The first argument may –for a large part– be overcome by using software of a very small size, only overwriting specific regions of memory. Furthermore, the software is permitted to use portions of memory it has already secured, allowing additional functionality to be introduced over time. Different stages and compression techniques can, therefore, be considered [4]. As for the second argument, not only may the integrity of the TCB, including the OS, pose difficult to predict beforehand, it may also prove problematic to determine a-posteriori.

Finally, as user-land programs are not allowed to read all (kernel) memory, the software needs to be installed with root privileges. Excluding a software-only approach in our scenario.

*Evaluation:* not applicable in our scenario. Although existing software scores high on the criteria of correctness, it scores relatively low on the criteria of atomicity and integrity [70, Tables 4.2, 4.3, 4.4].

#### 3.3 DIRECT MEMORY Access (DMA)

DMA allows components, other than the CPU, direct access to a computer's RAM and is used to speed up memory accesses by peripherals. Different external physical ports allow for DMA access. Exam-

ples are: PCI/PCIe [10, 14, 75]; PCMCIA, ExpressCard, PCCard [75]; FireWire [5, 12]; and Thunderbolt [62, 63]. Similar to software, the DMA method is performed on the same hardware from which the memory is acquired. Again allowing the method to be subverted by any of the components in its TCB [59]. DMA attacks may be mitigated through I/O Memory Management Unit (IOMMU) and OS protection mechanisms. The IOMMU acts as a kind of firewall, only allowing a device to read memory ranges specifically allocated to it. Recent OSes disable DMA once the device is locked<sup>1</sup>. Originally DMA only allowed for 32-bit addressing, therefore many DMA methods can acquire no more than four gigabytes of memory. Workarounds for this may require hardware or OS support, both of which cannot be applied in our scenario. Finally, the physical ports, e.g. Thunderbolt, may be unavailable, inaccessible or non-existent, and as some ports may not be hot-pluggable these may require pre-installation e.g. PCI/PCIe. These requirements exclude a DMA-only approach in our scenario.

*Evaluation:* not applicable in our scenario. Existing DMA methods score the lowest on the criteria of atomicity and integrity [15, 4.5.2.2 inception] when compared to other methods; its score on correctness is unclear.

#### 3.4 System Management Mode (SMM)

Multiple authors [57, 73] have opted to run software in System Management Mode (SMM) to acquire memory. Although the switch to SMM would halt other software and increase the method's atomicity, to obtain code execution in SMM one is required to either: (1) run software at the most privileged level; (2) pre-install the code to the BIOS chip and invoke it through a secure channel e.g. hardware switch; (3) patch the BIOS chip, reboot the system, and start executing own code from the reset vector.

The first possibility is not an option in our case. The second option is discussed in [57, 73], yet not applicable in our case due to its pre-installation requirement. The third choice defies the use of SMM for the most part, and other than running in SMM, is the same as the method discussed in the next section.

Evaluation: the same as BIOS modification in our case.

#### 3.5 BIOS MODIFICATION

Schramp has shown that a BIOS chip can be replaced whilst the system is still running [61]. By replacing the chip with one which houses

<sup>1 &</sup>quot;OS X Lion disables DMA when the user is logged out/screen is locked and FileVault is enabled. [...]" http://www.breaknenter.org/projects/inception/

SerialICE<sup>2</sup> Schramp was able to dump the computer's memory. SerialICE is software which allows one to: run a BIOS in the QEMU<sup>3</sup> emulator on one machine, and proxy all hardware accesses to the SerialICE mini shell running from the BIOS chip on another machine. By resetting the computer, it can be made to run the replacement BIOS's code from the reset vector. Schramp modified SerialICE such that it dumps the computer's memory directly after RAM initialization. The memory was dumped as ASCII hexadecimal Power-On Self-Test (POST) codes to a POST dongle. The POST codes are normally shown on a seven-segment display of a POST card indicating at what stage of self-test the BIOS is. The codes are typically used as extra information for troubleshooting, but allow for a slow communication channel. Gruhn [15, Section 5.5.2] attempted to reproduce the work of Schramp, yet was only partially able to do so. Gruhn was required to pre-install a BIOS chip socket such that the chip could be replaced without soldering.

Modifying the BIOS in general has been an active topic of research, often from the perspective of rootkit development [7, 8, 23]. This has led to the development of UEFI and Intel Boot Guard. The UEFI specification modernizes the older BIOS interface, and among other things, allows for cryptographic verification of firmware updates. Thereby preventing illegitimate modification of the firmware from the OS. However, implementations of the UEFI specification have proven to be vulnerable [3, 24, 26, 43]. To this end, Intel devised Boot Guard [29, 30]. Although the details on Boot Guard are scarce, the method seems to bind the integrity of contents of the BIOS chip to keys burnt into the hardware. Preventing illegitimate modification of said contents, which includes the firmware, as this check is performed on every power-on.

All in all, the suitability of this method is very platform-specific due to hardware specific initialization requirements and possible countermeasures. Therefore, this method may pose to be non-trivial to port to different platforms. Furthermore, because code execution can only be obtained through a reset (possibly depriving a computer's memory of power), the data remanence property (discussed in the next section) needs also to apply.

*Evaluation:* applicability conditioned on the presence of Intel Boot Guard and data remanence. Mixed results have been achieved during reproduction. We argue that BIOS modification scores high on the criteria of correctness, atomicity and integrity.

<sup>2</sup> https://www.serialice.com

<sup>3</sup> http://qemu.org/

#### 3.6 COLD BOOT

The cold boot method is based on the principles of memory retention (as discussed in Section 2.3), known in theory before but made famous thanks to the seminal paper of Halderman et al. [20]. Volatile SDRAM memory retains its state for a short period of time without power, cooling the memory increases this period. There are two general variants of this method. A first order cold boot attack, in which the same computer is reset to start acquisition software, typically loaded from a bootable device. A second order cold boot attack, in which the memory modules (DIMMs) are transplanted to a different computer which runs the acquisition software. Typically software such "memimage" as released by the original authors4 or "msramdump" by Wesley McGrew<sup>5</sup> is used to perform a cold boot attack. However, this software does have the same consequences described in Section 3.2; overwriting parts of the memory to be acquired. Even more so, Halderman et al. noted that: the BIOS may overwrite small parts of memory with its own code and data; destructive POST routines may destroy large chunks of memory; and ECC memory may be initialized entirely to a known initial state by the BIOS [20, section 3.4 BIOS footprints and memory wiping]. A more detailed discussion on these concerns is provided in Section 6.3.

As discussed in section 2.3, the period of time during which memory survives without power is labeled the retention period. Not all memory cells may survive over the whole retention period, some cells may decay faster than others. The length of the retention period is essential to the success of this method, yet depends on many different factors. Lindenlauf, Höfken, and Schuba [45] have identified the variables at play to be: SDRAM type; SDRAM manufacturer; individual SDRAM; cold boot mainboard; multi-channel mode; SDRAM temperature; and SDRAM time without power. Carbone, Bean, and Salois [9] have identified the physical properties underlying these factors to be related to the: memory density, residual capacitance of the cold boot motherboard, and resolution of the production process. A point we will return to in Section 7.3.

Over the years, mixed results in performing cold boot attacks have been achieved. Hannay and Woodward [22] set out to verify the work of Halderman et al., but were unable to find any remnants of data aside from data of the software used. Carbone, Bean, and Salois [9] were able find remnants of data, but only for some of the tested systems<sup>6</sup>. Gruhn and Müller [16] claimed that cold boot attacks on DDR2 are possible, DDR3, however, was deemed impossible to acquire using the cold boot method. Gruhn and Müller note that it is unclear

<sup>4</sup> https://citp.princeton.edu/research/memory/code/

<sup>5</sup> http://mcgrewsecurity.com/oldsite/projects/msramdmp.1.html

<sup>6</sup> Although extensive details of the computer systems tested are included, it is unclear from their work exactly which memory types have been tested.

whether the immunity of DDR3 is solely due to its construction type, or also owing to effects introduced by the memory controller. In a paper written from an engineering perspective, Liu et al. [46] have tested the retention times of 248 different SDRAM chips of thirty-four different DDR3 SODIMMs of five different vendors at various temperatures<sup>7</sup>. Through the use of an FPGA board and different testing patterns, they claim to have observed no memory cells with a retention time smaller than 1.5 seconds at 45°C. Strengthening the conjecture of Gruhn and Müller that the memory controller introduces detrimental effects. Lindenlauf, Höfken, and Schuba [45] have performed data retention experiments on fourteen DIMMs; both DDR2 and DDR3. Whereas the DDR2 experiments succeeded on a Gigabyte GA-G41M-Combo motherboard, the DDR3 experiments did not succeed on the same board. Nevertheless, the attack did work for DDR3 on the motherboard of a Asus P53E notebook. Leading the authors to claim that "[...] many boards overwrite DDR3 SDRAM with a random bit pattern during a cold boot.". Recently Bauer, Gruhn, and Freiling [2] verified that hardware vendors (e.g. Intel) have opted to apply memory scrambling. We suspect that, this hardware based memory scrambling has most likely been the cause of problems in reproducing the work of Halderman et al. on DDR3 as experienced in [16] and [45]. Memory scrambling will be discussed in greater detail in Part III.

It is good to note that, on the one hand, this method may well be the most destructive of all methods presented here. Any mistake in cooling or timing may result in only the ground state of the DIMM being acquired, not allowing for any second try. On the other hand, we argue that this method has the smallest TCB of all and that it may be applied in certain scenarios (e.g. ours) where other methods can not.

Evaluation: applicability conditioned on the presence of the remanence effect. Mixed results have been achieved during reproduction. The cold boot method scores the highest on the criteria of atomicity and integrity [15], yet the rate of decay may directly be related to the degree of integrity that can be achieved.

#### 3.7 LEGAL REQUIREMENTS

Owing to the fact that the acquisition method will most likely be used in a forensic context, it is of importance that data acquired is deemed to be reliable evidence in a court of law. To this end we provide an overview of the relevant jurisprudence and case law.

Typically, digital evidence of this nature is to be presented to the court by a expert-witness. In the Dutch case (which we focus on) an expert-witness may be registered in the nationwide expert-witness

<sup>7</sup> It is unclear exactly which chips of what DIMMs have been tested. Furthermore, the vendor names have been anonymized.

register<sup>8</sup> meant to assure the quality of the expert. However, this is not obligatory and it is up to a judge whether he allows one to act as an expert-witness. The Dutch law states: "De deskundige brengt aan zijn opdrachtgever een met redenen omkleed verslag uit. Hij geeft daarbij zo mogelijk aan welke methode hij heeft toegepast, in welke mate deze methode en de resultaten daarvan betrouwbaar kunnen worden geacht en welke bekwaamheid hij heeft bij de toepassing van de methode." [74] (emphasis by the author). The emphasis translates to: the expert-witness should –if possible– note which method was used and to which extent the results of the methods can be deemed reliable. Based on case law and Dutch jurisprudence ([25], [6, pp. 50-82], [54]) the following questions –that may be asked by a judge– have been formulated (translation by the author):

- I. What is the profession, education, and experience of the expert?

- II. Does the expertise of the expert extend to the matter at hand?

- III. Which method was used by the expert?

- IV. Were there other methods available? If so, then why was this method chosen?

- V. What is the reliability of the used method (motivation of)?

- VI. Was the expert able to professionally execute the method?

Only once a suspect challenges the findings of an expert-witness a judge is required to ask these questions. It is then up to the judge as to determine whether an additional expert is required to reach a conclusive verdict. The main problem in the scenario of volatile memory is the possible destructive application of any of the acquisition methods. In other forensic disciplines, the Netherlands Forensic Institute (NFI) has established forensics technical standards, these include procedures on the (possibly destructive) securing of biological traces e.g. blood or fingerprints. To the best of our knowledge, such standards have not been established in the digital context. We argue that the use of such a standard should also raise the confidence of a judge in a acquisition method in the digital domain, as its reliability in general will become more uniform.

To aid in this we put forth two appendices: Appendix B, in which a flowchart is presented, that may help a forensic investigator in choosing the most suitable method of memory acquisition; and Appendix C which discusses the procedure that should be followed once the acquisition presented in Part II has shown to be most suitable. We conclude that the reliability of the acquisition method of choice needs to be justified. We do this by reviewing applicable scientific literature (as provided in this chapter), and by discussing the method's implementation details and validating its forensic soundness in Part II.

<sup>8</sup> https://www.nrgd.nl/

<sup>9</sup> In the international context the (similar) Daubert criteria [69] have long been of the de facto standard.

#### 3.8 CONCLUSION

In a memory acquisition scenario, there are many factors involved that may vary widely. Some may be in one's own hands, whilst others may not. In the context of the predefined scenario, every method discussed in this chapter brings its own advantages and disadvantages to the table. By opting for a combination of the BIOS modification and cold boot methods, we aim to professionalize an acquisition method that is applicable even in the most worst-case of scenarios. Our hope is to produce a forensically sound acquisition method with a small TCB.

# Part II ENGINEERING COLD BOOT USING COREBOOT

4

#### 4.1 CONCEPT

The general concept is to use the cold boot method together with BIOS modification. It is known that the cold boot method does not work with certain BIOSes. Therefore, it is our goal to, on the one hand, have a BIOS that doesn't wipe or overwrite memory whilst, on the other hand, to implement additional (acquisition) functionality. This idea is not new, it has been thought of before by Appelbaum, one of the authors of the original cold boot paper:

"If you were to implement your own custom BIOS you would be able to, for example, dump the memory with having a very minimal amount of memory being stomped on. [...] With Coreboot someone, I think his name is Uwe and maybe Peter [Stuge], I forget, they implemented a small plugin for Coreboot that actually allows you to boot a machine that has this little plugin loaded and it simply dumps the memory to the screen and you can page through it." [1] (transcription by the author).

The functionality of the Coreboot plugin is present in the "core-info" payload of Coreboot under the name "RAM dumper"<sup>1</sup>. Stuge elaborated on the idea of Appelbaum by commenting:

"Because we're doing the RAM initialization we can stop right after RAM initialization is complete and do whatever we want, it's open-source so go ahead and have some fun. Do some special dump routines, we can even utilize another trick which is called Cache-as-RAM to not have to use any RAM at all so we can really extract every single byte of data that is in RAM." [64].

There are two main advantages of this concept over the available cold boot acquisition software such as "memimage" and "msramdump". First, Cache-as-RAM (CAR) should allow the acquisition of all memory, directly after memory initialization, without overwriting any of it. Second, the time the transplanted DIMMs are without power can be reduced by detecting the insertion of a DIMM from CAR.

To the best of our knowledge, a BIOS specifically developed for memory acquisition has not been implemented before. Therefore, we

<sup>1</sup> https://www.coreboot.org/Coreinfo

have developed a proof-of-concept implementation, the design and details of which will be discussed next.

#### 4.2 DESIGN

The acquisition method developed has been designed to minimize the time the DIMM is without power, and should thereby reduce the amount of decay introduced. The procedure for acquiring memory is as follows:

- I. Boot the acquisition machine without a DIMM and poll for the insertion of a DIMM

- II. Cool the DIMM of the target machine

- III. Transplant the DIMM from the target to the acquisition machine

- IV. As soon as the DIMM is inserted, the acquisition machine initializes and starts refreshing the DIMM

- V. The contents of the DIMM are secured to persistent memory of the acquisition machine

During the entire procedure nothing is overwritten in RAM as all code is running from CAR and the memory is acquired as soon as memory initialization has finished.

#### COREBOOT

Coreboot<sup>1</sup> is free open-source software and has been described as an open-source extended firmware platform. It is an alternative to the closed-source firmware and BIOSes developed by commercial independent BIOS vendors such as: Insyde, American Megatrends Inc, and Phoenix. Coreboot performs the minimal amount of hardware initialization possible to be able to execute a payload. Different payloads can be executed after Coreboot has initialized the hardware. Examples are: SeaBIOS (x86 BIOS implementation), TianoCore (UEFI implementation), a Linux kernel, or diagnostic tools (e.g. MemTest86). Coreboot's code is the first that runs on a computer<sup>2</sup>.

#### 5.1 BINARY SITUATION

Firmware contains large amounts of platform-specific hardware initialization code. Much of this is only provided as binary blobs by hardware vendors. Hence, open-source initialization code can only be developed by reverse engineering such blobs. This process is very time-consuming and the documentation of such code is arcane due to the lack of datasheets, as these are only available under Non-Disclosure Agreement (NDA) or are vendor confidential. Coreboot's choice to include blobs that are not (yet) reverse engineered is one of the reasons behind the Coreboot code-fork named Libreboot<sup>3</sup>. Libreboot aims to be completely blob free, but is only supported on a very limited set of devices because of this constraint.

# 5.2 MEMORY INITIALIZATION

The memory initialization code of modern architectures is an example of functionality only provided as a binary blob, without any source code e.g. Intel's Firmware Support Package [65, Chapter 4]. Fortunately, the memory initialization code of older platforms has been reverse engineered and for these platforms the source code is available. On the one hand, this allows us to take over execution directly after RAM has been initialised. On the other hand, although the code is open source, it is by no means easily understood. It con-

<sup>1</sup> https://www.coreboot.org/

<sup>2</sup> Before the reset vector the processor may have executed microcode updates or other logic such as the Built-In Self Test (BIST). Most of the time, this logic cannot be altered at all, or only by the hardware vendor itself through cryptographically signed updates. Therefore, it may be assumed integer.

<sup>3</sup> https://libreboot.org/

tains many 'magic' reads and writes from and to memory addresses and offsets thereof. Furthermore, public documentation in this topic is absent.

# 5.3 CACHE-AS-RAM (CAR)

Coreboot is able to run compiled C code before it has even initialized RAM. The motivation to run C code so early in the boot sequence, is based on the fact that assembly code is much more difficult to reuse and maintain across many different architectures. Originally Coreboot was only able to run C code so early in the boot sequence through the use of the ROMCC compiler. Because there is no RAM to save the stack, ROMCC used the processor's registers for this instead. By doing so, limits the code's functionality as it can keep only minimal state.

On more recent processors, Coreboot is able to use a mechanism named Cache-as-RAM (CAR) [41, 47, 53]. The terms no-fill mode [55] or no-eviction mode [76, Figure 15.1] are used by different literature interchangeably to refer to CAR. As the name suggests, CAR uses the processor's cache to save its state, as would normally be done in RAM. Although CAR is used in most recent BIOS implementations and all of the building blocks to enable it are public, to the best of our knowledge, Intel does not support nor provide any public documentation on the method as a whole. Furthermore, as with the reverse engineered memory initialization code, the code is not obvious and has been named "an esoteric area of the code" or "black magic" by Coreboot's developers.

To be able to verify and explain CAR's implementation, we have cross-referenced the available documentation with Coreboot's CAR-code for our architecture<sup>4</sup>. CAR works by altering the cache's operating modes [31, Volume 3A, Table 11-5, Cache Operating Modes]. MTRRs can to be set to change the cache its behaviour for certain memory ranges (as discussed in Section 2.2.1). CAR is in fact used by Coreboot for two purposes: (1) to save the stack; and (2) to speed up execution of the code that needs to be fetched from the BIOS chip, by loading it into the processor's cache. The first goal requires the cached data to be both readable and writeable, the second suffices with a read only region.

To enable CAR the following procedure is followed: all MTRRs are cleared, default caching type is set to uncacheable, a MTRR is set to control the memory range required, the MTRR is enabled, caching is enabled through the CPU's control register, either the region is cleared or the data is read from the BIOS chip (and thereby cached), and caching is disabled through the CPU's control register (actually enabling CAR).

<sup>4</sup> src/cpu/intel/model\_206ax/cache\_as\_ram.inc https://github.com/coreboot/ coreboot/blob/e74ad21a91e33f275a7bda999b058a8390c44ae6/src/cpu/intel/ model\_206ax/cache\_as\_ram.inc

#### IMPLEMENTATION DETAILS

#### 6.1 EXFILTRATION ROUTES

The acquisition method has been designed to acquire the memory very early in the boot sequence, because of this many, components have not yet been initialized. This poses an interesting challenge in either initializing an exfiltration route to another computer e.g. networking, or initializing a large portion of non-volatile memory e.g. a hard disk; both such that a copy of the volatile memory can be written to it and thereby secured.

As discussed in section 3.6, Schramp used post codes to extract the memory acquired. Actually working around this problem, as POST codes are typically routed by default to the Peripheral Component Interconnect (PCI) bus. However, this transfer channel is tediously slow<sup>1</sup>, and has never been designed with large data transfers in mind. To initialize another exfiltration route, the hardware device in question needs to be enabled and a driver is required to communicate with it. Here DMA becomes of great concern, as most modern transfer methods use DMA to increase their transfer rate. DMA uses RAM to buffer the data read and written without intervention of the processor. Typically the buffer is of a specific size. Output is written directly to memory and input may be directly read from memory. However, overwriting memory is not desirable in our case and in direct conflict with the forensic soundness of the acquisition method. Still, being able to read from the peripheral can be very convenient e.g. to read the file system's structure. Therefore, we have chosen not to use DMA although the problem could perhaps be alleviated by (temporarily) saving the memory to be overwritten in e.g. the cache.

The two exfiltration routes that have been explored by us are: (1) networking using an older PCI card that contains internal buffers²; (2) hard disk communication. The first had already been implemented in Coreboot, yet required more platform-specific code than anticipated. Due to the fact that PCI bridges not yet having been initialized at this point in the boot sequence. However, they are required to be correctly initialized, as otherwise data will not be routed to the correct PCI device. It proves non-trivial to initialize the bridges without access to sufficient memory.

Therefore, second, the option of using the SATA controller in Programmed I/O (PIO) mode has been investigated. Invoking the

<sup>1</sup> The same is true for the serial debug channel Coreboot provides.

<sup>2</sup> https://blogs.coreboot.org/blog/2010/05/31/coreboot-console-over-ethernet/

SATA initialization code of Coreboot at an earlier point in time, and combining it with the SATA PIO driver of SeaBIOS enabled us to use the hard disk to save the memory acquired. The main hurdle to overcome was finding the correct I/O base-port of the SATA controller. A rate of 100 MiB per minute has been achieved and was regarded to be sufficient.

#### 6.2 ACCESSING ALL MEMORY

The main part of Coreboot natively compiles as 32-bit code and runs in protected mode, this only allows one to address the lower 4 GiB of data (as discussed in Section 2.2). To address more memory, paging has to be enabled. Although, paging allows one to access all memory regions, the accessible memory is still limited to 4 GiB at a time. To access all memory, one additionally needs to either enable windowing or long mode. The application of windowing allows a range of low logical memory addresses (< 4 GiB) -named a window- to be translated through the paging mechanism to high physical addresses (> 4 GiB) such that the higher physical addresses may be accessed. Because this windowing introduces additional complexity in the acquisition routine, the option of running Coreboot as 64-bit code (in long mode) has been explored. However, due to Coreboot's non-trivial build system and numerous 32-bit truncated pointers, this would require significant effort to change. Although, there has been some previous work on enabling Coreboot to run as 64-bit code, this has been very experimental<sup>3</sup>. Therefore, our system uses windowing to acquire memory saved in high physical host addresses.

Enabling paging has also proven to be more of a challenge than anticipated; the main difficulties to overcome were the: (1) limited debugging options; (2) large number of different paging options; (3) space and alignment requirements of the paging tables; (4) combination of paging and CAR introducing unpredictable behavior. Although all of these problems can be overcome, their combination acts as a multiplier on the effort required to do so. Even more so, any of the latter three difficulties led to an unbootable system and therefore a tedious development cycle. Eventually the following options allowed us to access all memory. First, Coreboot allows for the use of a POST-card and serial debug output, the latter of which is not available until after CAR and the former only provides very rudimentary output. Second, by using Physical Address Extension (PAE) we were able to page 4 GiB of memory. Third, using PAE keeping the required paging tables small enough to save them in cache. The problem of size is increased as even small paging tables are required to be aligned on (large) page-boundaries, for this we used GCC's aligned variable attribute. Fourth, as all of the code is running from CAR, it is

<sup>3</sup> https://www.coreboot.org/pipermail/coreboot/2015-January/079135.html

essential that the activation of the paging-mechanism does not interfere with the system's caching behavior. However, every page can is accompanied by several flags that define its, amongst other things, caching properties. The combination of setting the: Present, Read/write, Accessed, Page size, and Global flags enabled us to use paging in CAR. This combination was found in the experimental 64-bit conversion previously discussed, see [31, Table 4-4. Format of a 32-Bit Page-Directory Entry that Maps a 4-MByte Page] for the meaning of these bits. Furthermore, the point in the boot sequence at which paging is enabled is of great importance. Enabling it before the Memory Controller Hub (MCH) has finished initialization causes the paging mechanism to stay disabled although the processor's control registers acknowledge that it has been enabled.

# 6.3 MEMORY INTEGRITY CONCERNS

As described in Section 2.2 memory addresses accesses may not always be routed to data in RAM, the MCH may decide to route to addresses to different components depending on its configuration. Furthermore, some components do not come with their own memory and use (overwrite) part of the computer's RAM to function (the 'stolen' memory regions). These are only two examples of concepts that may impact the integrity of memory to be acquired.

We have identified the following components and concepts that may reduce the integrity of the memory to be acquired. As the acquisition system of a second order cold boot method may route and translate parts of memory differently than the target system, this is of particular importance in our case. The list is by no means restrictive and may be different for every platform, yet it should provide a decent overview of the concepts that may need to be taken into account:

- Memory overwrites i.e. the BIOS writing data to RAM

- Destructive POST routines i.e. destructive memory training/test-ing

- Reserved BIOS regions<sup>4</sup>

- Memory Type Range Registers (MTRRs)

- Memory regions stolen by the:

- Internal graphics device

- SMM

- Intel ME (see Appendix D)

- Memory scrambling (as discussed in Part III)

<sup>4</sup> The stock BIOS on our system reports 150 MiB to be unusable or reserved. This was observed by executing the dmesg command on a default Ubuntu installation.. These memory regions are, for example, not acquired by the "memimage" software released by Halderman et al. [20].

Most of these problems are inherently countered by our acquisition method. Because it acquires memory directly after memory initialization, before any other functionality is used. Only the devices stealing memory regions required explicit disabling. We chosen not to disable any of the memory training/testing routines, as this is required for the correct initialization and communication with the memory modules.

# 6.4 REPRODUCIBILITY

All source code to reproduce any of our results can be found as a Coreboot patch at https://review.coreboot.org/#/c/18539/.

7

#### VALIDATION

To validate whether the method developed is actually forensically sound, we verify whether it meets the requirements as set out in Chapter 3. Therefore, we verify whether it complies with the properties of correctness, atomicity, and integrity as defined by Vömel (and Freiling). Due to the use of the cold boot method, atomicity is implied, hence our focus is on correctness and integrity. Correctness is implied when a complete copy of all data present in the physical DIMM is acquired i.e. no memory ranges are skipped/missed. Integrity is implied when the contents of memory is not altered after the start of acquisition method e.g. due to loading the acquisition program into memory or decay due to the cold boot method. It may be the case that a property is not fulfilled completely, it is then still desirable to determine the degree of fulfillment. Performing the following experiment has allowed us to determine this.

# 7.1 EXPERIMENT METHODOLOGY

We employ a similar experiment as defined in [16, section II. Setup - C. Experiment]. The experiment comprises three steps: 1) filling the memory with reproducible pseudo-random data, 2) executing the acquisition method, and 3) measuring the difference between the data acquired and the expected pseudo-random data.

As opposed to the experiment defined in [16, section II. Setup - C. Experiment], we chose to differ two of the conditions. First, a different cooling method has been chosen to determine whether the original cooling technique could be improved upon (professionalized). Second, instead of executing the experiment on only relative small amounts of data e.g. 2 MiB in [16], the experiment has been performed over all data that the DIMM could hold e.g. 1 or 4 GiB such that the degree of correctness of the method as a whole could be determined. The details of the setup used have been attached as Appendix A.

#### 7.2 COOLING TECHNIQUES

In general the cooling of memory modules is done through the use cooling spray, either dedicated freezing spray or ad-hoc upside down canisters of compressed air. By spraying this directly on the memory modules, the DIMMs are brought down to a temperature of between the  $-30^{\circ}$  and  $-50^{\circ}$  Celsius. Although this method is widely accepted

[2, 16, 20, 45], it may have severe consequences. First, the flash freezing of electrical components may cause them to malfunction. The locating of thermal faults in electrical equipment is one of the typical use-cases of freeze spray. Second, the formation of frost and subsequent condensation may cause component malfunction. Although the widespread use of freeze spray to perform the cold boot method may suggest otherwise, this is a well known side-effect of extreme cooling in the field of overclocking. Either of these consequences may result in loss of the data to be acquired.

We have, therefore, chosen to explore a different method of cooling. As noted, much experience with extreme cooling in this context may be drawn from the overclocking scene. The use of liquid nitrogen evaporation coolers is one example hereof. This type of cooler consists of a heatsink which clamps around the DIMM with a tray on top that holds the liquid nitrogen. An image of its usage is attached in Appendix A as Figure 11. As the liquid nitrogen evaporates, it cools the tray and heatsink drastically, which in turn cool the DIMM. The benefits of the method are threefold: (1) the memory can be cooled to extreme temperatures in a reduced pace as the mass of the heatsink prevents fast temperature fluctuations; (2) frost collects nearly exclusively on the heatsink instead of the DIMM. The heatsink can be removed as soon as the memory has been transplanted, reducing the risks related to condensation; and (3) The DIMM can be cooled to even extremer temperatures (around  $-150^{\circ}$  Celsius).

We have made no further attempt to professionalize the cooling method, but directions to explore may be: a closed circuit cooling system connected to the heat sink; or working in a humidity (and temperature) controlled environment, with enough space to execute the entire method in. The former of which is already commercially available to the overclocking community<sup>1</sup>.

#### 7.3 DISCUSSION OF EMPIRICAL RESULTS

The experiments we have performed, show high rates of decay for most of the DIMMs tested (irrespective of the cooling method applied). In Appendix A a table is attached containing the details of the DIMMs tested. Of the four different DIMMs tested, only DIMM D has led to sufficiently low and reproducible decay rates<sup>2</sup> to base any findings on. This has led to the fact that we are unable to draw any strong conclusions on the general susceptibility of DIMMs to data remanence; allowing more work to be done in this area. Three observations are, however, deemed worthy of a discussion.

<sup>1</sup> See, for example, the OCC-X and Purge Case products of L&L Cooling Technologies http://www.lnlcooling.com

<sup>2</sup> The overall percentage of bits that either decayed was around 0.05%

First, the sole DIMM exhibiting low decay rates is of the Small Outline DIMM (SODIMM) type, typically used in laptops. Leading us to believe that their physical construction may be more susceptible to data remanence due to their reduced power usage i.e. longer retention rates mean less refreshes in turn using less power. This suspicion is strengthened by the fact that many of the studies that are successful in reproducing the cold boot attack focus on SODIMMs [20, 45, 46]<sup>3</sup>.

Second, it is unclear when a DIMM's capacitors are being refreshed. The DIMM is controlled by the DIMM's internal finite state machine. During normal operation the MCH ensures the DIMM is refreshed. However, it is unclear how removing an reasserting power influences the state machine of a DIMM.

Third, cryogenically freezing the DIMM may cause memory initialization to fail. Cooling the DIMM to extreme temperatures has resulted in the fact the DIMM could not be initialized correctly and only being able to do so after some period of time that allowed the DIMM to warm up again.

Taken together, although prior work showed mixed results, the extreme deviation between the retention time of different memory modules of the same DDR generation was an unexpected result. This should be taken as a note of caution for anyone considering to apply the cold boot attack in a forensic context. Nonetheless, we have still been able to validate the correctness and integrity of our method by performing experiments on the sole DIMM sufficiently susceptible to the remanence effect.

## 7.4 CORRECTNESS

We were able to verify the correctness of the method by executing the experiment defined in Section 7.1. This has allowed us to verify all memory physically present on the DIMM is acquired, and that no memory regions are missed.

#### 7.5 INTEGRITY

In spite of our extensive efforts to ensure no data in the DIMMs is overwritten, transplanting memory still causes certain regions of memory to be overwritten. The regions are typically located in the low address range from address 0x0 to 0x10000. We expect this behavior to be caused by the training routines or memory initialization, as the size of the memory regions differ based on the size of the DIMM initialized. Furthermore, as discussed in Section 7.3 the integrity of the method is directly related to the decay of the memory modules.

<sup>3</sup> Although the pictures from [45] suggest otherwise, to the best of our knowledge the DDR3 modules tested in the work of Lindenlauf et al. are of the SODIMM type.

#### 7.6 CONCLUSION

We argue that the method presented in this chapter has 'upped the ante' regarding the level of professionalization of the applicable memory acquisition methods. The application of the concept of CAR, acquiring memory directly after its initialization, disabling stolen memory regions, and experimentation with a different method of cooling, has allowed for the development of a acquisition method with a high degree of correctness.

Nevertheless, it showed to be far more difficult than expected to verify the claim of integrity, as the underlying cold boot method has shown much greater levels of deviation in the remanence period between different DIMMs than expected. Concluding, this results in a acquisition method of which its forensic soundness is directly influenced by the underlying physical properties influencing the remanence period of a DIMM.

# Part III RESEARCH THE INTEL MEMORY SCRAMBLER

8

#### **BACKGROUND & GOALS**

#### 8.1 BACKGROUND

As noted in Section 3.6 Cold boot, recent computer architectures include a component which scrambles the data sent over the memory bus. The reason for including this scrambler is to prevent signal integrity issues due to power spikes on the power supply. The power spikes are introduced when writing many successive ones or zeroes are written to memory [28, 2.1.6 Data Scrambling]. The switching required between a zero and a one on the memory bus would, most likely, be the cause of this; a well known relation in the field of sidechannel power analysis attacks. For example, the physical representation of a logical one may be a high voltage, whereas a logical zero may be represented by a low voltage. Due to comparable deteriorating effects, similar scrambling techniques are also applied in many other high capacity wired and wireless transmission protocols e.g. SATA, USB3, PCIe and CDMA. The scrambler works by mixing-in a source of pseudo-randomness, before the data is transmitted. At the receiver's side this pseudo-randomness is removed again.

Typically the pseudo-randomness required by such a scrambler is based on the output of an LFSR (see Figure 4), due to its small implementation size and good statistical properties. The output of an LFSR is called a Pseudo-Random Binary Sequence (PRBS). An LFSR consists of a register (its state) with multiple entries, every entry contains a single bit. With every shift (or clock) of the register one bit is shifted out (output bit) and one bit is shifted back into the register (feedback bit). The feedback bit is produced through a combination of specific entries of the register. LFSRs have two main advantages; 1) LFSRs are very efficient to implement in hardware and 2) can be defined in a mathematical sense by expressing them using GF(2) (matrix) arithmetic. These two advantages have led to their wide implementation and study. The output of a LFSR repeats after a certain number of clocks, this number depends on the size of the register and feedback polynomial in use. A scrambler can be seen as a stream 'cipher' i.e. the PRBS is generated completely defined by the LFSR's internal state. The LFSR's initial state is called a seed. The idea is to XOR the data with a PRBS which consists of approximately an equal amount of ones and zeroes. This increases the number of switched bits on average, yet prevents the worst case scenario of only zeroes or ones to occur. Instead of the term cipher, henceforth, the term scram-

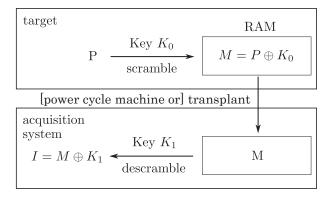

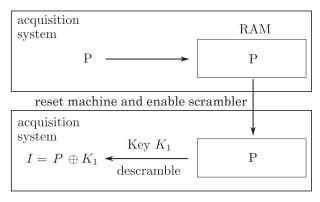

Figure 4: Schematic overview of a typical scrambler. A PRBS is produced by an LFSR and combined with the data to obtain the scrambled data. The same system can used for descrambling. The internal state of this LFSR is 1010 at the moment.

bler is used, as such a scrambling system is in no way meant to be cryptographically secure.

The main problem introduced by the scrambler is that, when the PRBS is not known, scrambled data may not easily be descrambled. Normally the scrambler performs its scrambling entirely transparent, all data sent will be received by the same scrambler with the same state. However, because the PRBS is generated based on an initial (random) seed on every boot, this may cause problems when executing the cold boot method to acquire memory. The memory to be acquired may be scrambled with the PRBS generated based on one seed, and may be descrambled with a PRBS generated based on another seed. Leaving the resulting memory image incomprehensible. This problem may intensify when different versions of scramblers are used to scramble and descramble the data.

## 8.2 GOALS